aramısı

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

### ARAMiS II – Project Overview

SPONSORED BY THE

Prof. Dr.-Ing. Dr. h. c. Jürgen Becker, Karlsruhe Institute of Technology (KIT)

#### Electronic Components & Systems

Smart Smart Factory Grid Smart Mobility

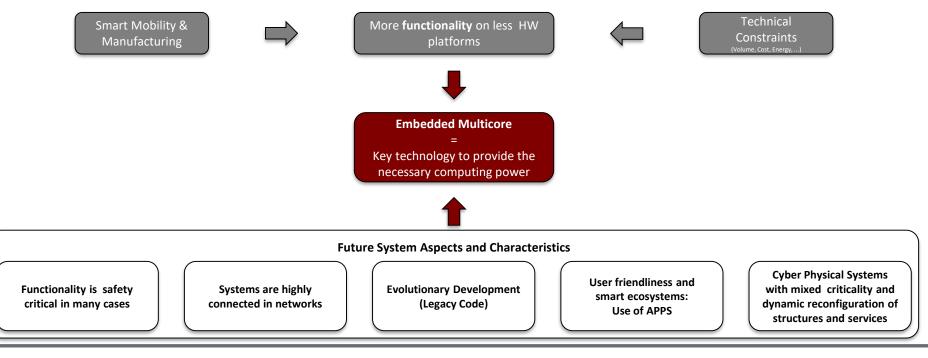

#### Increase of Electronic Systems (HW + SW) is required

- ... to integrate additional features

- ... to meet environmental challenges

- ... to enhance competitiveness

- ... to improve cost efficiency

#### Degree of automation will directly depend on embedded computing power !

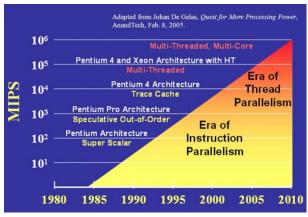

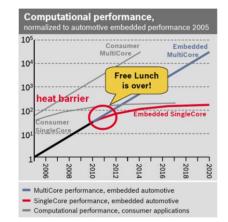

- Singlecore will not provide enough computing power in the future (scaling is over)

- Multicore is the best known solution that is able to provide sufficient performance

[Source: The Quest for More Processing Power: "Is the single core CPU doomed?", Johan De Gelas, 2006]

[Source: The Challenge of Mastering Parallelism in Real-Time Systems, J. Haerdtlein, 2014]

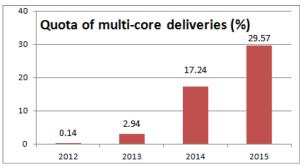

Quota of deliveries based on multi-core CPU at VW/AUDI (not yet in safety critical applications):

<sup>[</sup>Source: Shared SW development in multi-core automotive context, L. Michel, et. al, 2016]

- Singlecore will not provide enough computing power in the future (scaling is over)

- Multicore is the best known solution that is able to provide sufficient performance

# But: Multicore comes with challenges ...

# Common resources shared between different execution units can lead to system dysfunction (loss of functions / malfunctions) caused by:

- Time interferences (determinism issues)

- Space interferences (segregation issues)

- Common Cause Failures (e.g. SEE, electronic fail)

- Race Condition (Time-of-check vs. Time-of-use)

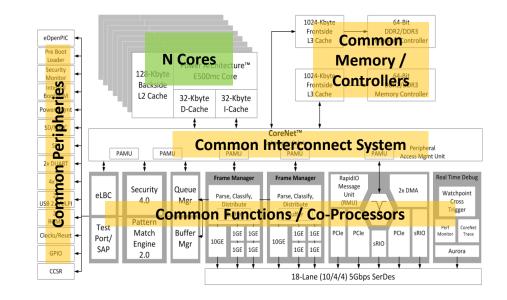

#### Issues depend on multicore architecture:

- Mono-Bus / Multi-Bus / Crossbar / NoC / etc.

- Core local memory or only shared memory

- Lock-Step-Mode core / end2end ECC / etc.

# Mitigations needed for safe and secure usage (per SW or HW):

- Failure Detection: Monitoring, Voting

- Failure Isolation: Partitioning, Time Slicing / Deadlines, Budgeting

- Failure Correction: Function Recovery, Redundancy, Architectural Patterns

#### Summary on Results of ARAMiS

- Improvement of Basic Software Architectures

- Improvements of platforms on system, hardware and software level.

- First Results on holistic tool support

- Work on Methodologies

- Prototypical implementations and evaluations in laboratory setups

- Demonstrators as feasibility studies and proof for deployment of multicore systems in real industrial environments

**ARAMIS** proved successfully the applicability of multicores in Safety-critical applications in principal...

... but uncovered further challenges in multicore development

Presentation of ARAMiS Results at CeBIT 2016, Hannover

#### From ARAMiS to ARAMiS II

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

ARAMIS proved the applicability of multicores in safety critical applications in principle

# ➡

ARAMIS II targets the efficient use of multicores in safety critical applications in practice by preparation of:

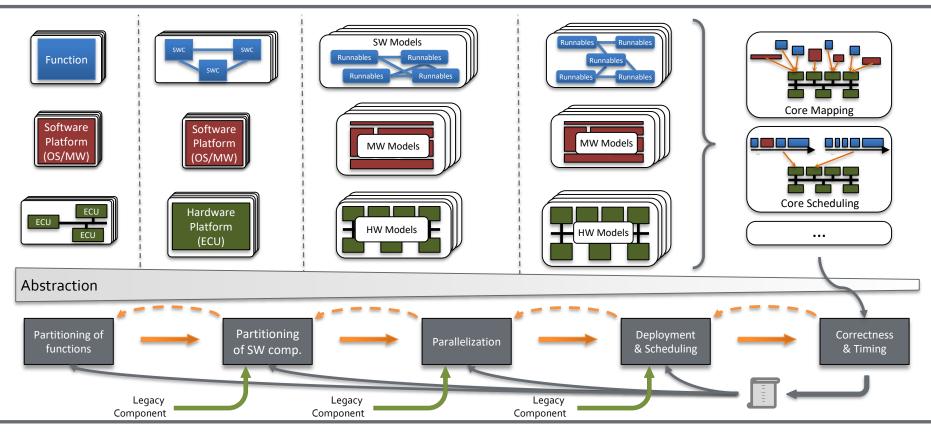

- 1. Separated steps in multicore development are not sufficient for a structured development of multicore-based systems

- **Process:** How could a superior (generic) multicore development process look like?

- **Continuity:** How can continuity in the process be achieved and which artefacts are needed?

- 2. Available methods and tools are not sufficient to master the complexity in the development of multicore-based systems

- Partitioning: When and where to split and distribute functionality?

- Allocation: Which could be the right platform for a certain application scenario?

- **Binding:** Which deployment of (basis-) software components is the most optimal solution?

- Scheduling: Which schedule of software can be run most efficiently?

- **Guarantees:** How can platform aspects (e.g. WCET, Safety, Security, correctness) be ensured?

- Design Space: How can a design space exploration be performed in such complex systems?

- 3. Well established platform standards and software architectures are not supporting the requirements of multicore-based systems (e.g. segregation, synchronization, communication)

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

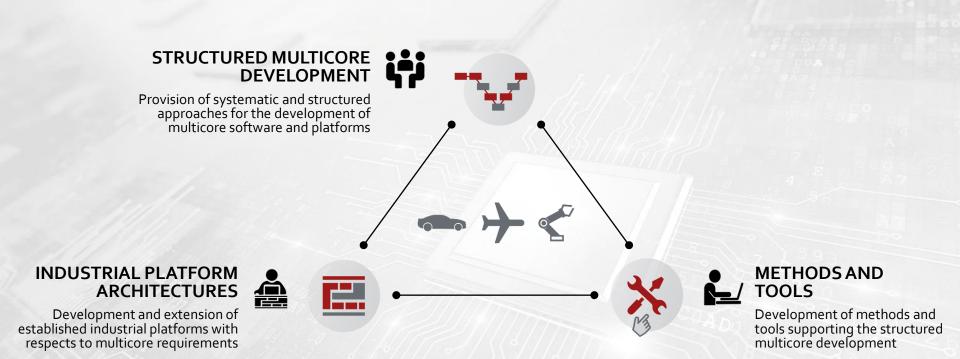

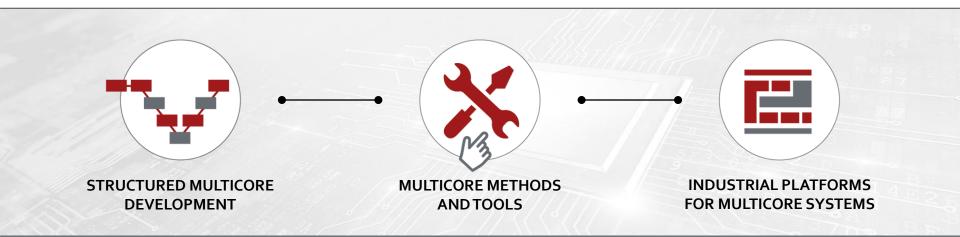

Summarized Working Focus and Project Goals

#### Scientific and Technical Approach

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

Project Overview | ARAMiS II Multicore Konferenz in Stuttgart | Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

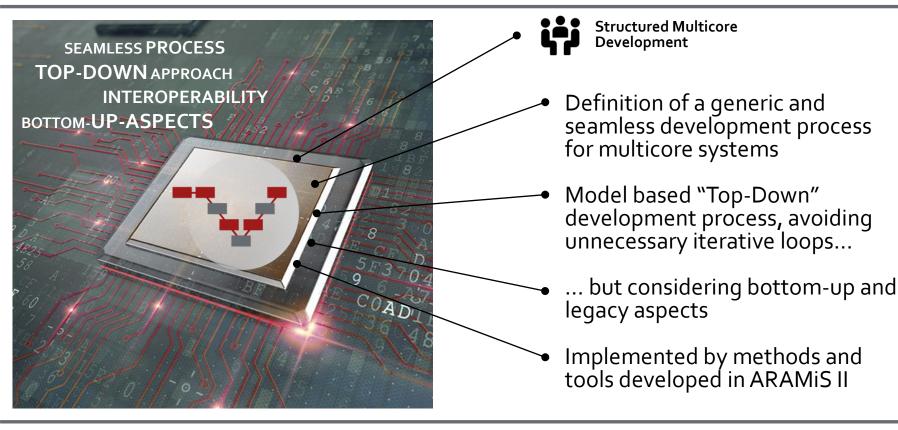

#### Subproject 2: Structured Multicore Development

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

Subproject 3: Multicore Methods and Tools

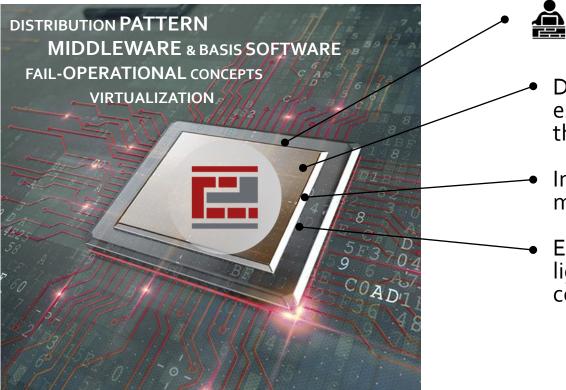

### Subproject 4: Industrial Platforms for Multicore Systems

Industrial Platforms for Multicore Systems

- Development and extension of established industrial platforms for the use in multicore-based systems

- Investigation of basis software, middleware and operating systems

- Evaluation and development of lightweight fail-operational concepts for multicore platforms

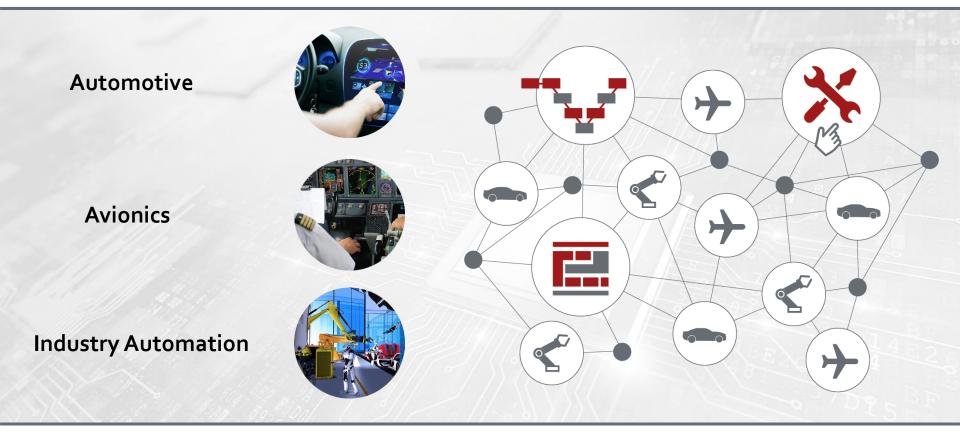

#### Involved Domains for the Validation of the Results

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

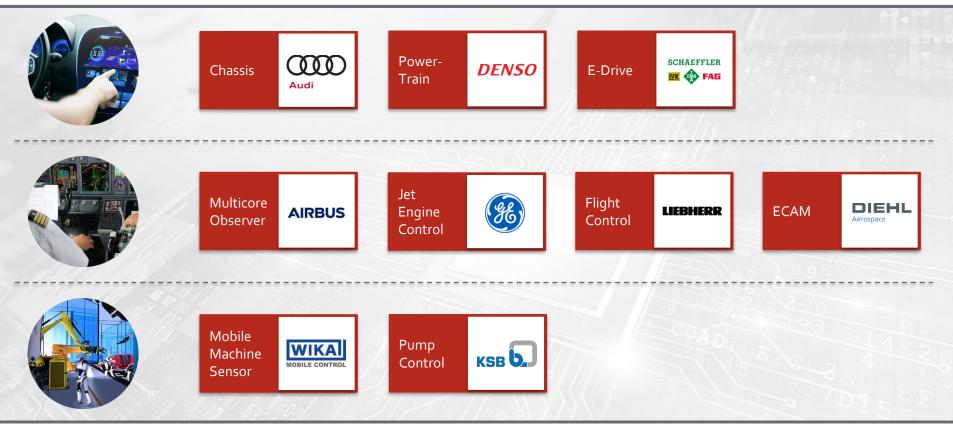

#### Subproject 5: Use Case Implementation and Evaluation

DEVELOPMENT PROCESSES I TOOLS I PLATFORMS FOR SAFETY-CRITICIAL MULTICORE SYSTEMS

Project Overview | ARAMIS II Multicore Konferenz in Stuttgart | Prof. Dr.-Ing. Dr. h. c. Jürgen Becker

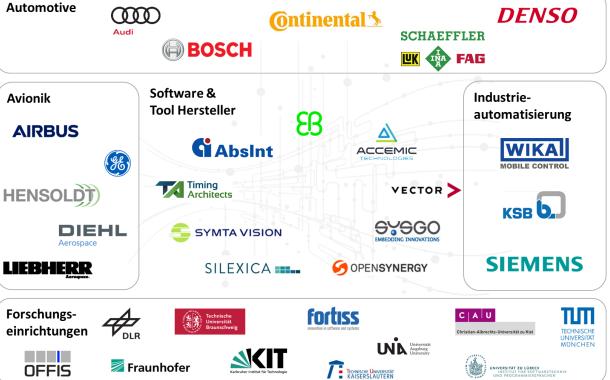

### Facts and Figures

- Technology (KIT)

Duration:

10/2016 09/2019

- Consortium: 33 Partner

- **Budget:** > 26 Mio.€

- Web:

www.aramis2.de

and Research

Publications up to now:

>40 (www.aramis2.de/publikationen)

FUNDED BY:

PROJECT MANAGEMENT AGENCY:

**DLR** Projektträger

6/22/2018

ENTWICKLUNGSPROZESSE I WERKZEUGE I PLATTFORMEN FÜR SICHERHEITSKRITISCHE MULTICORESYSTEME

## Thank you for your attention!

Prof. Dr.-Ing. Dr. h. c. Jürgen Becker (becker@kit.edu), Dr.-Ing. Falco Bapp (bapp@kit.edu)

Institut für Technik der Informationsvereinbarung (ITIV)

Karlsruher Institut für Technologie (KIT)

Engesserstrasse 5, 76131 Karlsruhe